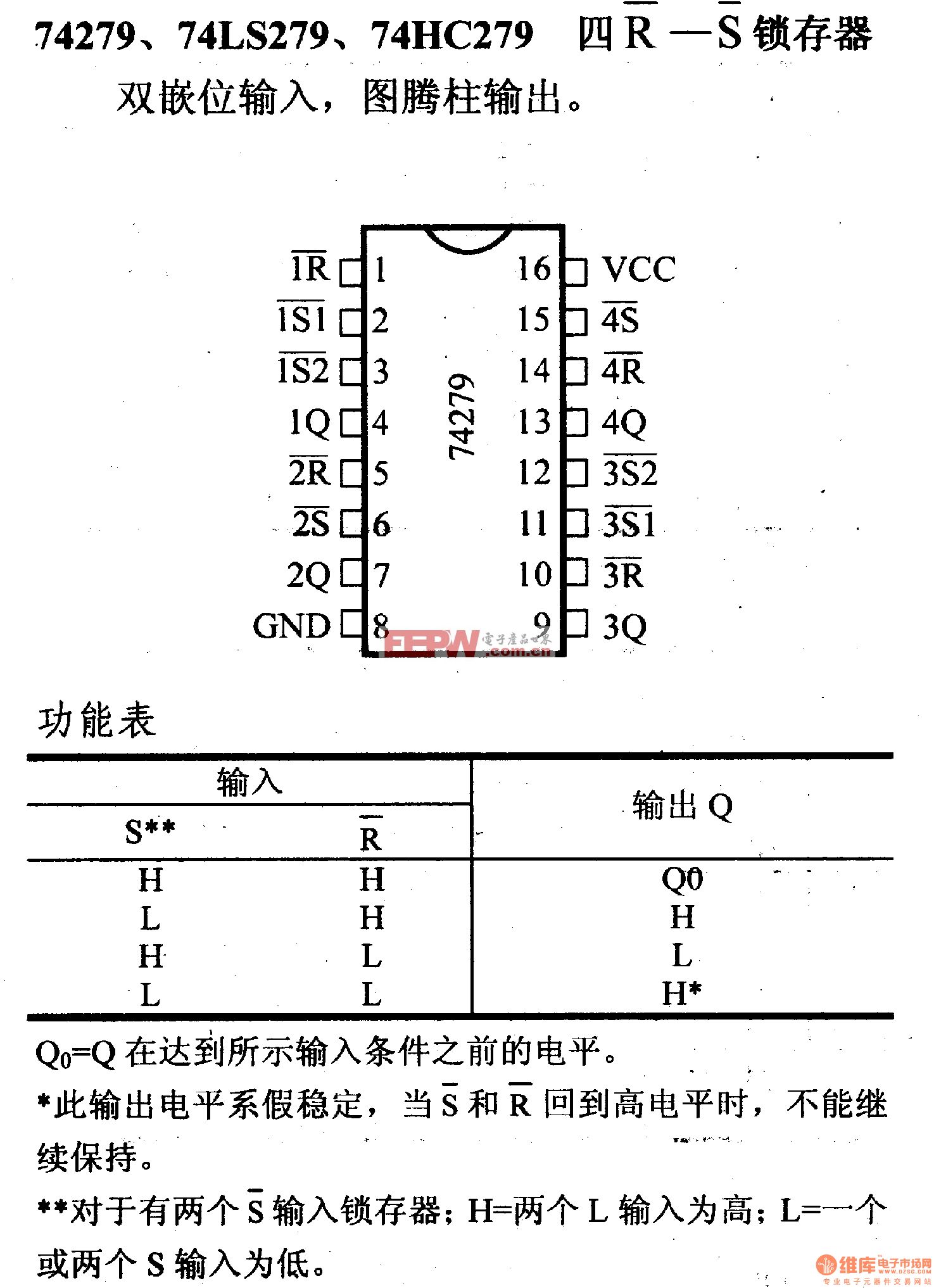

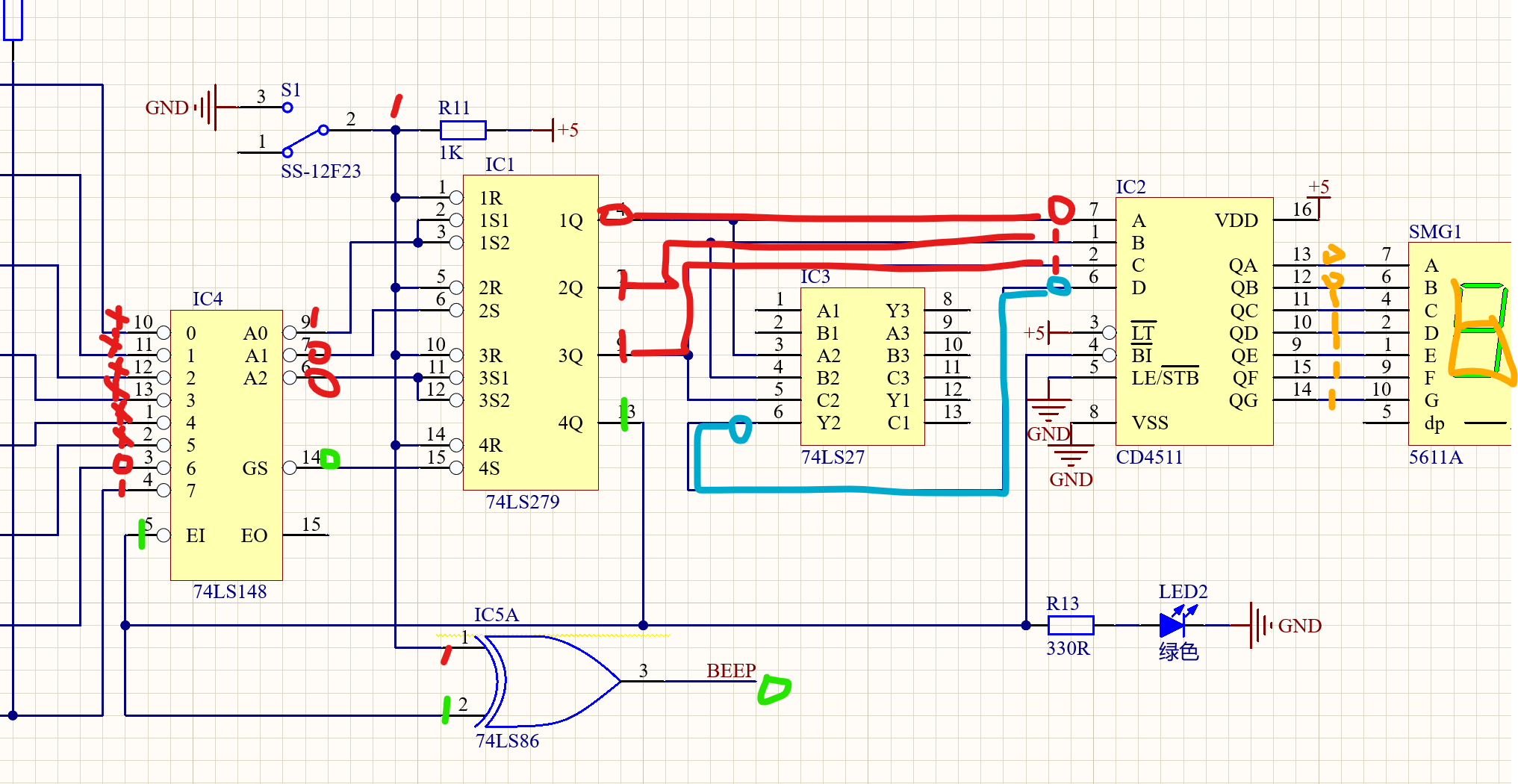

74ls279n引脚图及功能

|

4位双向移位寄存器图6

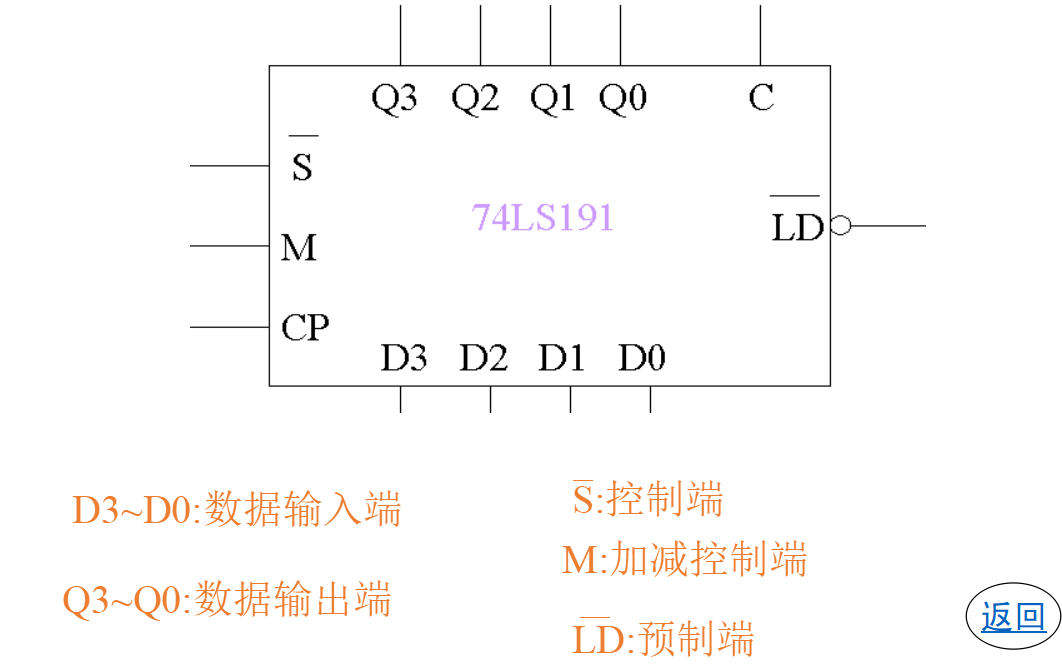

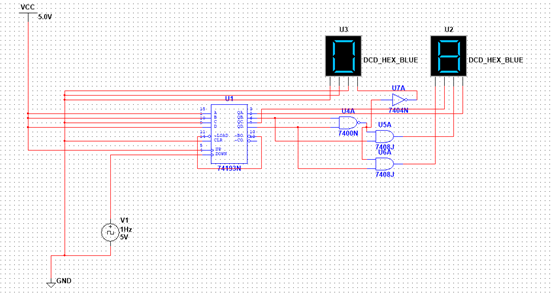

用4位二进制同步可逆计数器74ls191构成12翻1小时计数器

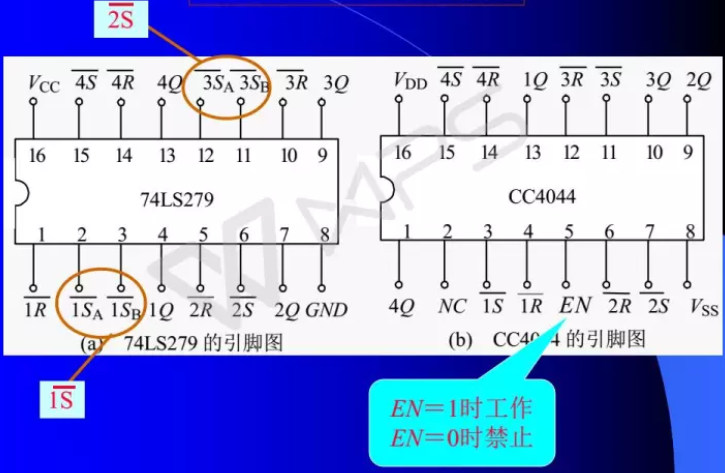

74系列数字电路7427974ls279等四rs锁存器

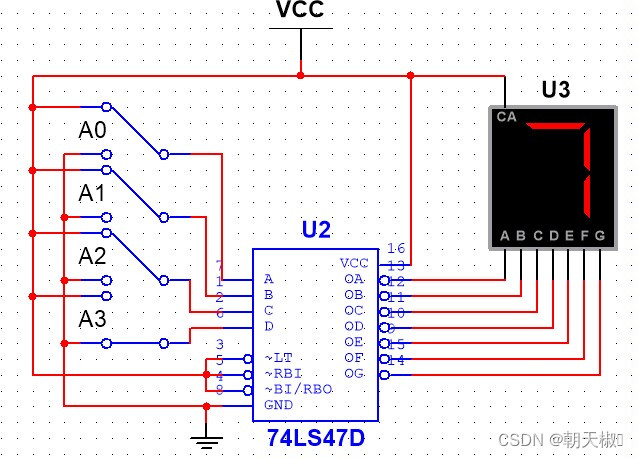

74138,74139,7447,74147,74151,74153

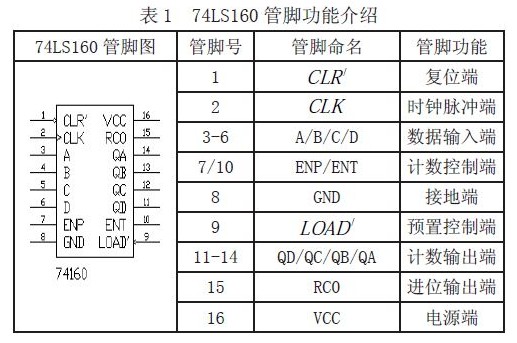

74ls160 逻辑功能见表2

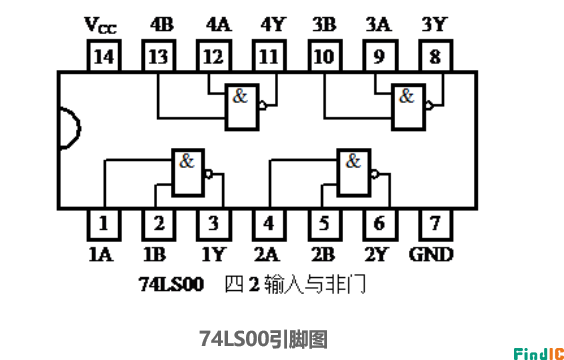

sn74ls00n引脚图

74ls198 74ls199 7422 ttl

4位并行加法器(74283n),异或门(74ls86n),灯泡(probe)实验思路:a,b

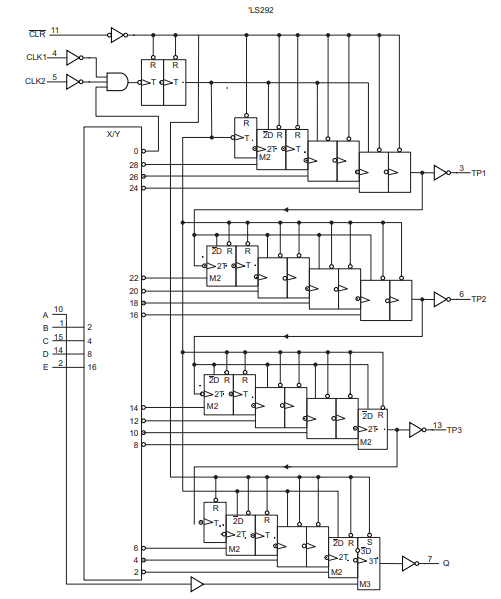

逻辑符号引脚配置易于扩展可用频率范围为 dc 至 30 mhz(sn74ls292 为

74ls系列数字电路功能解释:8421码成电路用74ls90芯片轻松搞定(4)

当开关闭合时,rs触发器(74ls279)的复位端r,置位端s均为0,4个触发器

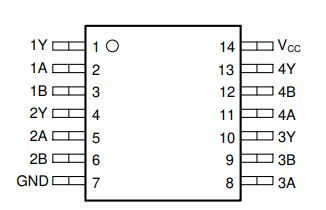

工程科技 信息与通信 常用芯片引脚排列图 常用芯片引脚排列图 74ls48

74163清零端构成的12进制计数器 其引脚图如图1所示

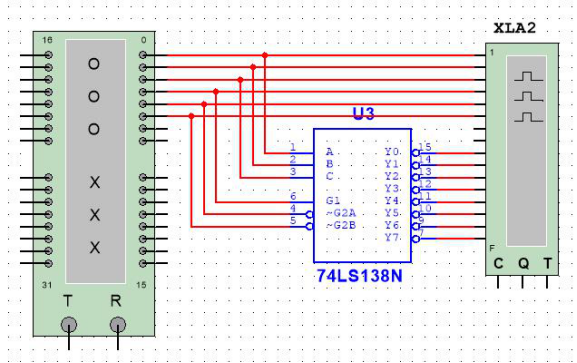

逻辑门对半加器进行电路设计和仿真验证译码器74ls138n的逻辑功能三

引脚配置61与lstl逻辑ic相比,功耗显著降低61支持扇出多达10个

ne556n 集成电路ic芯片电子元器件集成块直插dip14

图6

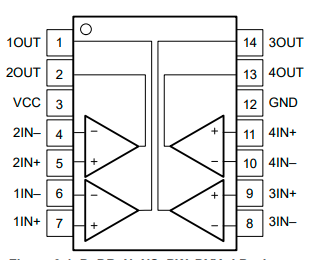

dr2g/lm339pwr/lm339n中文资料规格书pdf档手册引脚图

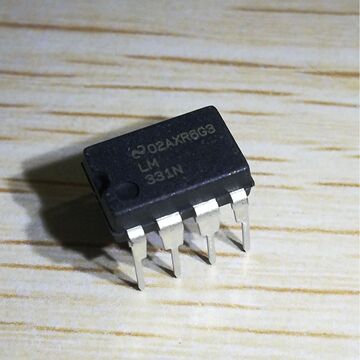

lm331n 集成电路ic芯片电子元器件集成块直插dip8

全新74ls153 sn74ls153n hd74ls153p dip

原装拍一件=5个 sn74ls153n dip16 双4选1数据选择器芯片 2v~6v

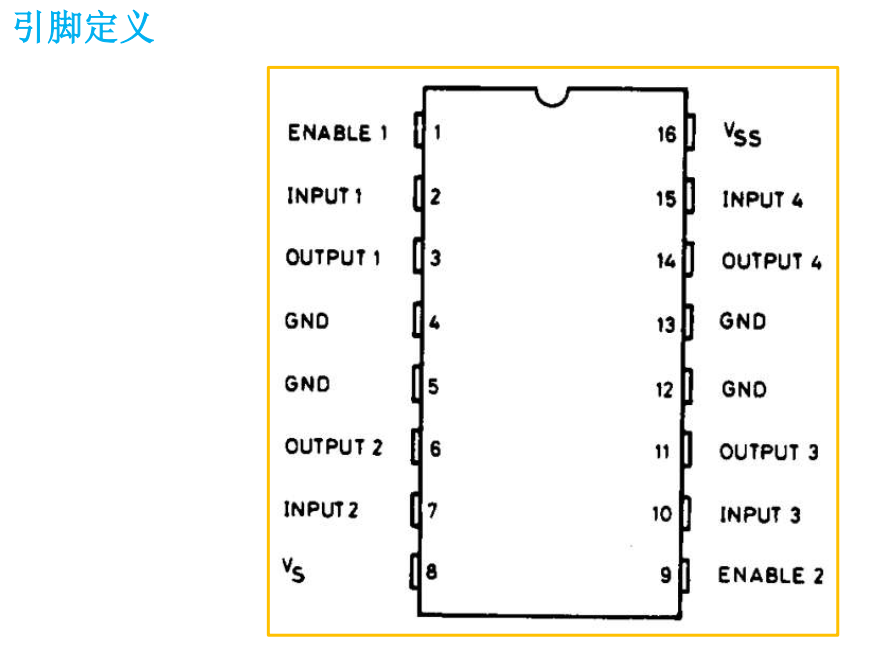

引脚定义一一一一一一一一一一一一一一一一一一一一一一一一一一一

4rs触发器是有的,74ls279就是

逻辑芯片 sn74ls279n 74ls280 283 290 293 295 299 595 323 393n

7400n是什么元件,它的3d图

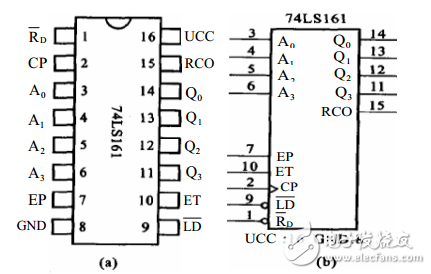

74ls161的引脚排列和逻辑功能如图1所示各引出端的逻辑功能如下

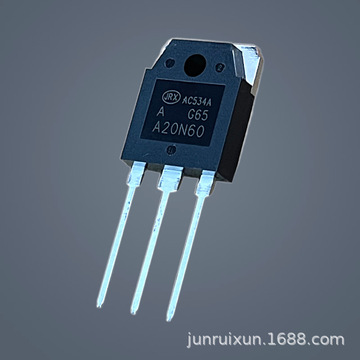

jra20n60 20n60 600v 20a mos管 晶体管 用于充电器 开关电源

74ls192功能表

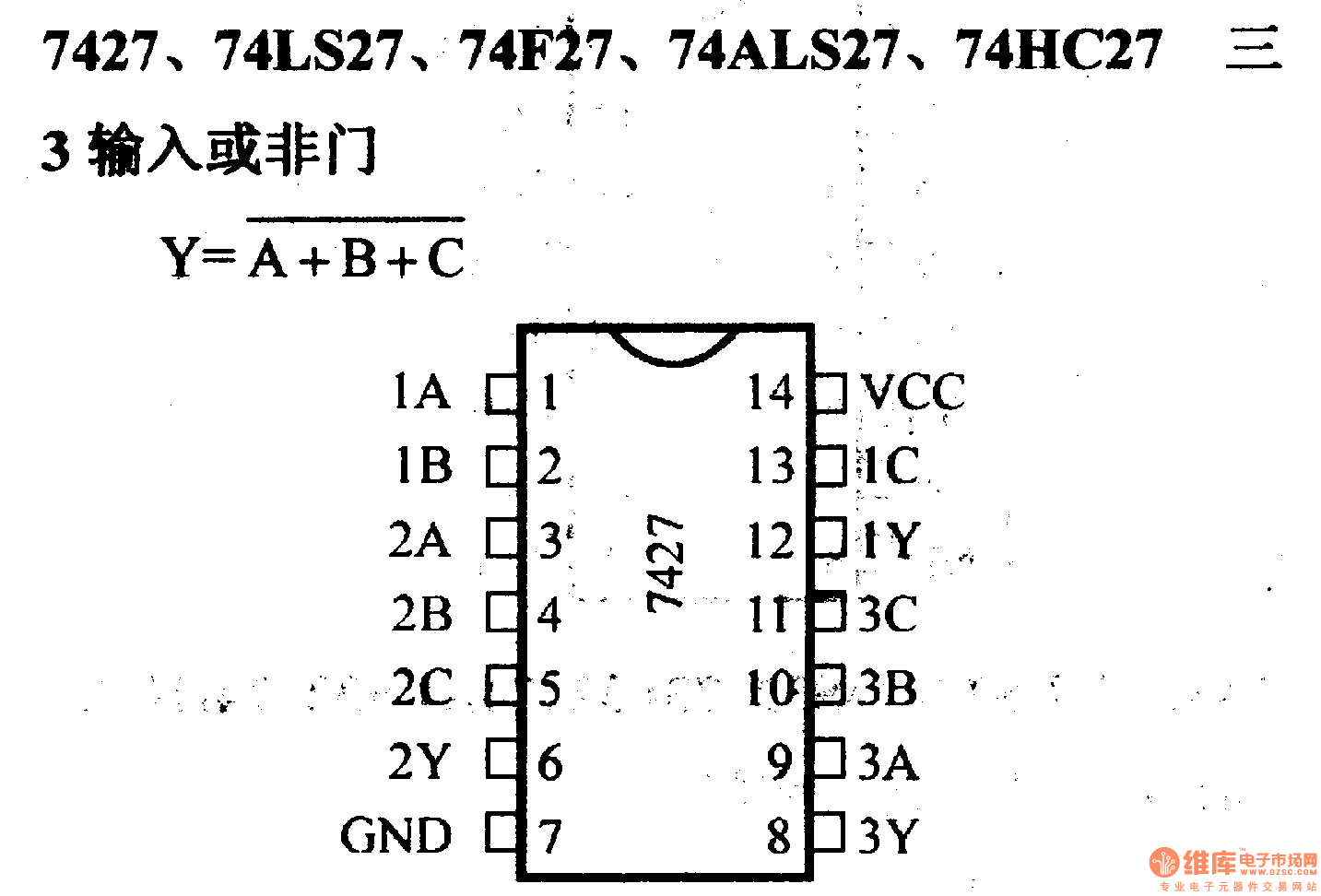

74ls27等三3输入或非门

基本rs触发器的特点7,波形图6,状态图5,特性方程4,次态qn 1的卡诺图3 |